Scientists Find Too Many Cooks Er Cores Spoils The Cpu

Too Many Cooks Spoil the CPU: Understanding the Performance Pitfalls of Over-Coring

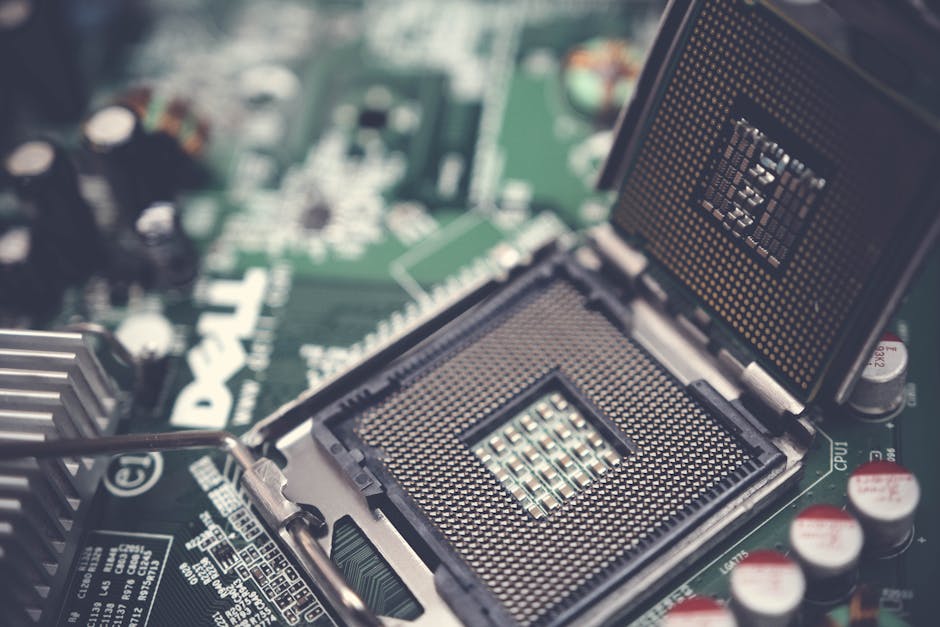

The relentless march of technological advancement in the semiconductor industry has consistently pushed the boundaries of computing power. A key metric in this evolution has been the increasing number of cores integrated into a single Central Processing Unit (CPU). This trend, driven by the promise of parallel processing and enhanced multitasking, has led to a bewildering array of processors boasting eight, sixteen, thirty-two, and even hundreds of cores. While intuitively, more processing units should translate to superior performance, a growing body of evidence and practical experience suggests a counterintuitive reality: too many cooks can indeed spoil the CPU. This phenomenon, where an excessive number of cores can lead to diminished performance, decreased efficiency, and increased complexity, warrants a deep dive into the underlying technical reasons and the practical implications for consumers and industries alike.

The fundamental concept of multi-core processing relies on the ability of a CPU to divide tasks among its independent processing units, executing them concurrently. This parallel execution is highly effective for workloads that can be naturally fragmented into smaller, independent sub-tasks. Examples include rendering complex 3D scenes, scientific simulations, video encoding, and large-scale data analysis. In these scenarios, having more cores allows for a significant reduction in processing time as multiple cores work on different parts of the problem simultaneously. However, this ideal scenario is not universally applicable, and several limiting factors emerge as core counts escalate beyond a certain threshold for specific applications and system architectures.

One of the primary bottlenecks that emerges with over-coring is the issue of inter-core communication and synchronization. As the number of cores increases, so does the complexity of coordinating their activities. Cores often need to share data or synchronize their progress, and the mechanisms for this communication become increasingly strained. This communication overhead, while often negligible with a few cores, grows exponentially with more cores. Each core requires access to shared resources like cache memory, system memory, and I/O interfaces. As more cores contend for these limited resources, the likelihood of contention and the need for complex locking mechanisms to prevent data corruption increase significantly. These locking mechanisms introduce delays, as one core may have to wait for another to release a shared resource. This serializes parts of the execution that were intended to be parallel, negating the benefits of additional cores.

Cache coherency protocols represent another critical area where over-coring can introduce performance penalties. Modern CPUs employ multi-level cache hierarchies (L1, L2, L3) to reduce memory access latency. When multiple cores access and modify the same data, ensuring that all cores have the most up-to-date version of that data becomes a complex challenge. Cache coherency protocols (e.g., MESI) are designed to manage this, but as the number of cores increases, the overhead associated with maintaining coherency grows. The "snooping" or "directory-based" mechanisms used for coherency require constant communication between cores and cache controllers, leading to increased bus traffic and latency. In an extreme scenario with too many cores, the time spent maintaining cache coherency can outweigh the time saved by parallel execution.

The scalability of software is arguably the most significant factor dictating the efficacy of high core counts. Not all applications are designed to effectively leverage parallelism. Many legacy applications, or those with inherently serial dependencies, cannot be broken down into independent threads of execution. For these applications, adding more cores to the CPU will yield little to no performance improvement. In fact, the overhead introduced by the operating system in managing a large number of cores and scheduling threads across them can even lead to a slight performance degradation. The "Amdahl’s Law" is a fundamental principle that highlights this limitation, stating that the speedup achievable by parallelizing a task is limited by the serial portion of the task. If a significant portion of a program must be executed sequentially, then even an infinite number of processors will not lead to infinite speedup.

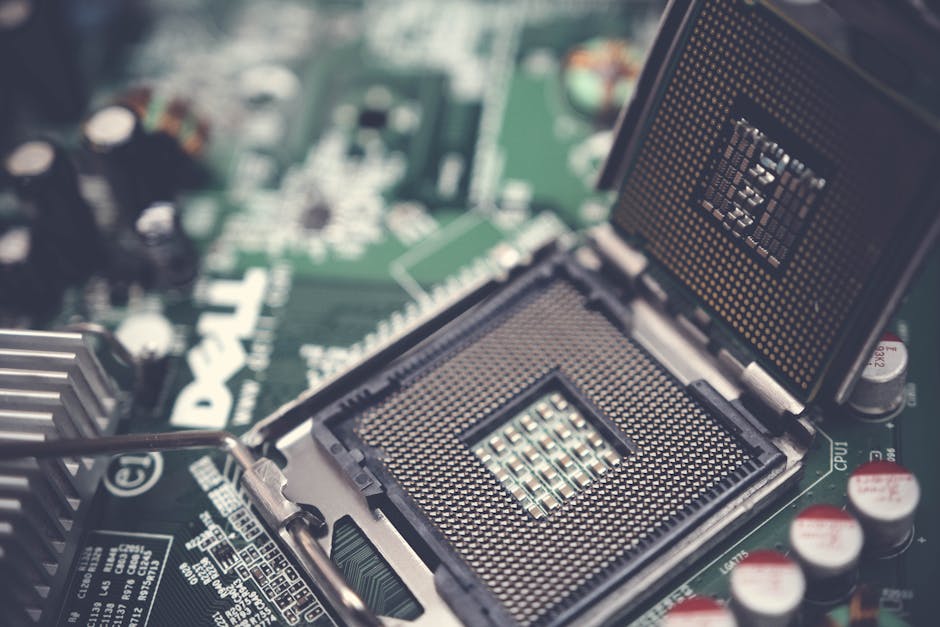

Furthermore, power consumption and thermal management become increasingly challenging with higher core counts. Each active core consumes power and generates heat. As the number of cores increases, the total power draw and heat output of the CPU escalates dramatically. This necessitates more robust cooling solutions, which can add to the cost and complexity of a system. More importantly, to manage heat and prevent damage, the CPU may throttle its clock speed, reducing the performance of all cores to keep within thermal limits. This phenomenon, known as thermal throttling, can effectively negate the performance gains expected from a high core count processor, especially under sustained heavy workloads. The power delivery system also needs to be more robust to supply sufficient power to a large number of cores, further contributing to system complexity and cost.

The cost-effectiveness of high core count processors is another crucial consideration. While the manufacturing cost of a single transistor has decreased, the complexity and yield challenges associated with integrating hundreds of cores onto a single die can significantly increase the price of high-end CPUs. For many common use cases, the performance gains from a moderate number of cores (e.g., 4-8 cores) are more than sufficient, and the premium for significantly higher core counts may not be justified by the marginal performance improvements. This is particularly true when considering the software limitations previously discussed. A user running a typical desktop operating system with standard applications like web browsing, office productivity, and light multimedia consumption will likely not experience any tangible benefit from a 64-core processor compared to a 16-core one, and may even incur higher energy costs.

The memory bandwidth and latency also become potential bottlenecks in heavily multi-cored systems. While more cores can process data faster, the rate at which data can be fetched from or written to main memory (RAM) can become the limiting factor. If the memory subsystem cannot keep pace with the demands of numerous cores, the cores will spend significant time waiting for data, hindering overall performance. This is often addressed with larger and faster cache hierarchies, but these also contribute to increased die size, power consumption, and cost. For certain workloads, specialized memory solutions or architectures designed to maximize memory bandwidth might be necessary, adding another layer of complexity and expense.

The operating system’s role in managing a large number of cores is also critical. The OS scheduler is responsible for distributing threads across available cores. While modern operating systems are adept at this, managing a very large number of cores can introduce scheduling overhead. The OS needs to manage thread states, context switches, and load balancing, all of which consume CPU cycles. For applications that don’t scale perfectly, the overhead of OS management can contribute to the performance degradation observed with over-coring. The efficiency of the OS scheduler in distinguishing between high-priority, performance-critical threads and background tasks becomes paramount.

In conclusion, while the pursuit of increased processing power through higher core counts is a natural progression, it’s essential to recognize that more cores do not inherently equate to better performance for all workloads. The diminishing returns associated with inter-core communication, cache coherency overhead, software scalability limitations, power and thermal constraints, and memory bandwidth bottlenecks can all contribute to a scenario where "too many cooks spoil the CPU." For consumers and professionals alike, understanding the specific requirements of their applications and workloads is crucial when selecting a processor. A balanced approach, prioritizing efficient architecture and appropriate core counts for the intended use, will ultimately lead to more optimal performance, better power efficiency, and greater cost-effectiveness than simply opting for the processor with the highest number of cores. The focus should shift from a simple core count race to a more nuanced consideration of the entire system architecture and software ecosystem.